System SW and Its Machine Dependency 시스템 SW 및 해당 종속성

- 시스템 소프트웨어의 설계는 실행되는 기계(= 컴퓨터)의 아키텍처에 크게 영향을 받음

- 예를 들어, 어셈블러는 니모닉 명령어를 기계어 코드로 변환

- OS 는 컴퓨팅 시스템의 리소스를 직접 관리

- 시스템의 특정 구현은 시간이 지남에 따라 변경되지만 기본 개념은 변경되지 않음

- 시스템 소프트웨어의 기본 구조와 설계는 기본적으로 대부분 컴퓨터에서 동일

- 예를 들어, 모든 기계 아키텍처의 어셈블러 일반적인 디자인과 로직은 거의 동일

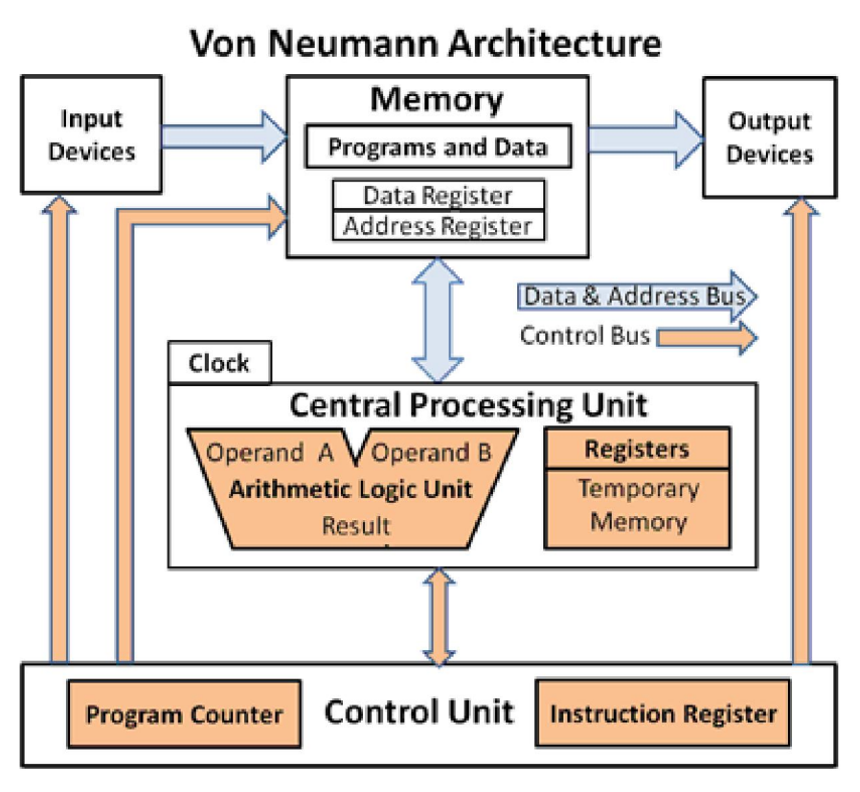

Computer Organization and Design: A Reminder 컴퓨터 구성 및 디자인: 리마인드

- 컴퓨터의 5가지 고전적인 구성요소: 입력, 출력, 메모리, 데이터 경로, 제어, 마지막 두개를 결합하여 프로세서라 부름

- 이것은 컴퓨터 아키텍처의 일반적인 구성요소

Computer(= Machine) Architecture

- 간단한 컴퓨터 구조

- 메모리 장치에는 프로그램(= 명령어 시퀸스)와 데이터가 포함

- CPU는 ALU를 통해 명령을 실행하여 프로그램을 실행

- ALU는 수학적 및 논리적 연산을 수행

- 제어 장치는 CPU의 동작을 정리하고, 다른 구성 요소의 동작을 시퀀싱하여 프로그램을 실행

- “Fetch-Decode-Execute” cycle

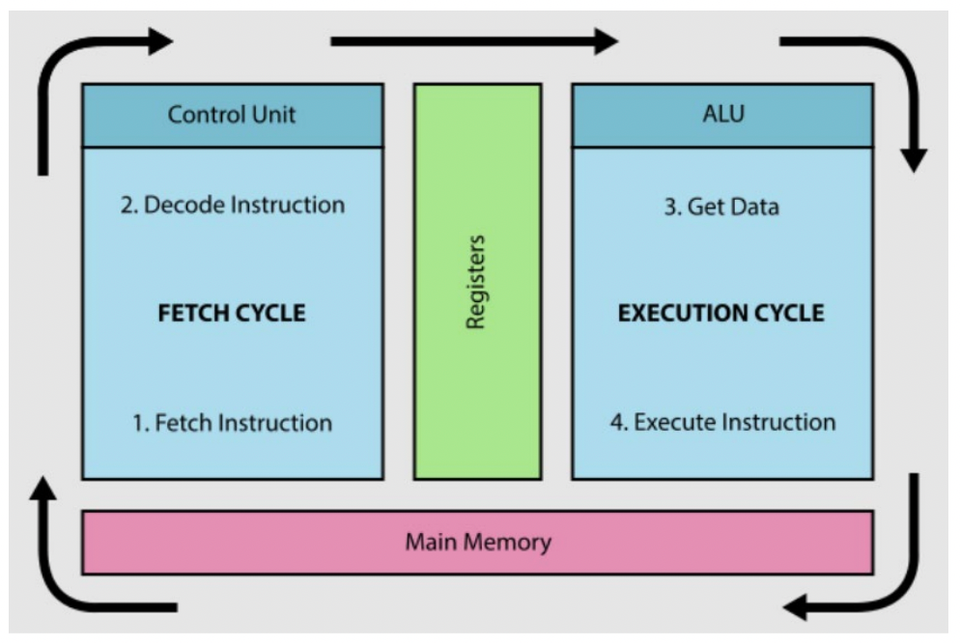

The Fetch-Decode-Execute Cycle

- 프로그램의 마지막 명령(보통 HALT, STOP, QUIT)에 도달할때 까지 다음 3단계를 계속 반복

- Fetch: 메모리에서 실행될 다음 명령어 가져오기

- Decode: 디코딩(= 수행할 작업 결정)

- Excute: ALU, 메모리 및 I/O 컨트롤러에 적절한 명령을 실행하여 실행

SIC(Simplified Instructional Computer)

- 실제 시스템에서 가장 자주 볼 수 있는 H/W 기능을 포함하는 가상의 컴퓨터, 특이하거나 관련 없는 복잡성은 제외

- 시스템 소프트웨어의 기본 개념을 이해하기 위해 특정 구현 세부 사항과 분리

- 상위 호환성이 있는 두가지 버전 존재

- SIC: 표준 모델

- SIC/XE: eXtra 장비(또는 고가) 모델

- SIC용 프로그램은 SIC/XE 시스템에서 실행가능

SIC Machine Architecture 1

- 일반 메모리

- 메모리는 주소가 0에서 시작하여 해당 배열에 대한 인덱스 역할을 하는 큰 1차원 배열일 뿐

- Cells 이라고 하는 고정된 크기 단위로 나뉨, 각 Cell은 주소라는 고유 식별자와 연결

- 위치 주소를 지정하기만 하면 메모리의 모든 위치에 매우 빠르게 액세스 가능

- 프로그램(및 데이터)은 실행될 때 주 메모리에 저장

- RAM은 데이터를 한 곳에서 다른 곳으로 매우 빠르게 이동할 수 있는 방식으로 CPU에 연결

- SIC 메모리

- 8비트 바이트로 구성: 3-byte words (24bit)

- 일반적인 컴퓨터는 4-byte

- 사용가능 최대 메모리: 32KB(2^15Byte)

- 8비트 바이트로 구성: 3-byte words (24bit)

<간단한 예시>

전체 크기가 32KB 이걸 2^15승으로 바꿀 수 있음

15는 메모리 주소를 표현하는데 필요한 비트 수

SIC Machine Architecture 2

- 일반 레지스터

- 임시 데이터를 저장하는 데 사용되는 CPU 내부의 개별 고속 저장 장치

- 일부는 특정 목적을 위해 전용되고, 다른 일부는 계산 중에 임시 저장소로 사용

- SIC 레지스터

- 5종류 특수 목적 레지스터

- A(0): Accumulator. 기본 산술 연산용

- X(1): Linkage register. 주소 지정을 위한 인덱스 값 저장용

- L(2): Program Counter. 특정 메모리 주소 저장/점프용

- PC(8): Program Counter. 실행할 다음 명령어의 주소 저장용

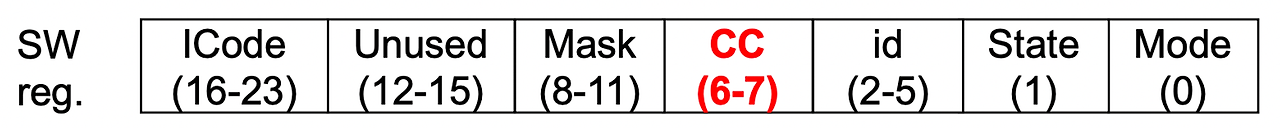

- SW(9): Status Word. 비교 및 조건부 점프 명령에 사용되는 CC(조건 코드) 비트 등 다양한 정보 저장용

- 5종류 특수 목적 레지스터

SIC Machine Architecture 3

- 데이터 형식

- 정수는 24비트 이진수 형태로 저장

- 음수 값은 2의 보수 표현 사용

- 일반적인 현대 컴퓨터 시스템과 동일

- 문자는 8비트 아스키 코드 형태로 저장

- 부동 소수점 하드웨어 없음

- 정수는 24비트 이진수 형태로 저장

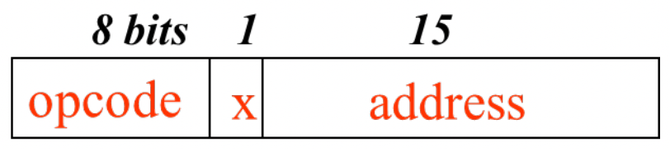

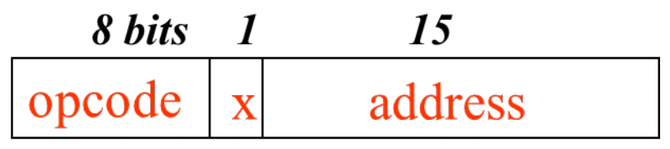

- 기계 명령어 형식

- SIC 표준 버전의 모든 명령어는 24비트

- 8bit opcode, 1bit x, 15bit address

- Operation code field: 하드웨어가 인식하는 각 기계 언어 작업에 할당된 고유 번호(부록 A 참조)

- Address field: 작업이 작동할 값의 메모리 주소

- SIC는 오직 1개의 포멧 소유

SIC Machine Architecture 4

- 일반적인 주소 지정 모드

- 레지스터에 저장된 정보 및/또는 기계 명령어에 포함된 상수를 사용하여 피연산자의 유효(= 대상) 메모리 주소를 계산하는 방법을 지정

- 레지스터에 저장된 정보 및/또는 기계 명령어에 포함된 상수를 사용하여 피연산자의 유효(= 대상) 메모리 주소를 계산하는 방법을 지정

- SIC의 주소 지정 모드

- Direct addressing mode: flag bit x = 0

- Target Address = Address

- Indexed addressing mode: flag bit x = 1

- Target Address = Address + X(레지스터 X의 값, (명령의 'x'비트가 아님)

- Direct addressing mode: flag bit x = 0

<간단한 예시>

SIC에는 어드레싱 모드가 2개가 있음, 이 어드레싱 모드에 따라 피연산자의 주소를 계산할 수 있음

피연산자의 주소를 계산할 수 있어야하고, 이 어드레싱 모드에 따라 계산됨

X 레지스터에 값을 저장해두고 Address에 더하여 타겟 주소를 저장

SIC Machine Architecture 5

- 명령어 집합(일반)

- CPU가 인식하고 실행할 수 있는 기계 코드로 된 모든 명령의 완전한 집합

- 프로세서에 필요한 작업을 지시하는 명령을 제공

- 주소 지정 모드, 명령, 네이티브 데이터 유형, 레지스터, 메모리 아키텍처, 인터럽트, 예외 처리 및 외부 I/O를 정의

- “ISA(Instruction Set Architecture)”라고도 함

SIC Machine Architecture 6

- SIC에서 제공하는 기본 명령어 집합

- Load or Store: LDA, LDX, STA, STX

- LDA m ? A ← (m .. m + 2), 여기서 A와 m 은 레지스터 A와 메모리(3Byte)를 나타냄

- 각각 주소는 메모리 위치 m ~ m+2의 내용이 레지스터 A에 로드되도록 지정

- STA m ? m .. m + 2 ← (A)

- 레지스터 A의 내용이 주소 m으로 시작하는 word에 저장되도록 지정

- Integer Arithmetic operations 정수 산술 연산: ADD, SUB, MUL, DIV

- ADD m ? A ← (A) + (m..m+2)

- SUB m ? A ← (A) - (m..m+2)

- MUL m ? A ← (A) * (m..m+2)

- DIV m ? A ← (A) / (m..m+2)

- 모든 산술 연산은 레지스터 A와 메모리에 있는 단어를 포함하며, 결과는 레지스터 저장

- Load or Store: LDA, LDX, STA, STX

SIC Machine Architecture 7

- SIC에서 제공하는 기본 명령어 집합

- Comparison 비교: COMP

- COMP m ? (A) : (m..m+2), 레지스터 SW에 CC코드를 저장하여 값 표현

- 레지스터 A의 값을 메모리에 있는 단어와 비교하고, 레지스터 SW의 조건 코드(CC)를 설정하여 결과를 나타내는 것을 의미

- < → 01 bits, = → 00bits, or > → 10 bits

- Conditional Jump 비교 점프: JLT, JEQ: JGT

- CC 설정을 테스트하고 그에 따라 점프

- JLT m ? PC ← m if CC set to <

- JEQ m ? PC ← m if CC set to =

- JGT m ? PC ← m if CC set to >

- Comparison 비교: COMP

<간단한 예시>

기본적으로 COMP 연산은 A레지스터와 메모리 값의 데이터의 비교하고 CC 필드에 상태를 저장

CC 필드에 있는 값이 비교 결과 값

CC 필드의 설정 결과 값에 따라 비교 점프를 실행하여 m의 위치로 이동하여 명령 실행

분기를 만드는 코드

PC ← m : PC 레지스터에 m 메모리 주소 저장, 이후 PC에 저장된 m 명령을 실행

SIC Machine Architecture 8

- SIC에서 제공하는 기본 명령어 집합

- Subroutine linkage: JSUB, RSUB

- JSUB m ? L ← (PC); PC ← m

- JSUB는 서브루틴으로 점프하여 레지스터 L에 주소를 배치

- RSUB ? PC ← (L)

- RSUB는 레지스터 L에 포함된 주소로 점프하여 반환

- Subroutine linkage: JSUB, RSUB

<간단한 예시>

JSUB, RSUM 모두 코드 플로우 조작

JSUB은 메서드를 호출하는 것과 유사, 코드 블럭을 나누는 용도(SUB Routine)

일단 무조건 점프해서 m에서 실행

서브루틴을 마지막에는 무조건 RSUB가 있음, 메소드의 리턴과 유사

JSUB → 서브루틴 코드 실행 → RSUB

JSUB를 실행하면 JSUB의 다음 코드 주소 값이 L에 저장, 서브 루틴 시작 주소 값은 메모리에서 PC로 이동

서브루틴 코드 실행 후 RSUB을 만남

RSUB이 실행되면 L에 저장된 주소로 다시 돌아함

돌아갈 주소값을 저장하는 레지스터 L

SIC Machine Architecture 9

- SIC에서 제공하는 기본 명령어 집합

- – I/O (Input and Output) 입출력

- 레지스터 A의 맨 오른쪽 8비트 사이에서 한 번에 1바이트씩 전송하여 수행

- 각 장치에는 고유한 8비트 코드가 할당

- 3가지 명령어: TD (test device), RD (read data) , WD (write data)

- TD m ? (m)에 의해 지정된 장치가 데이터 바이트를 전송 및 수신 준비가 되었는지 테스트

- 장치가 준비되면 레지스터 SW의 CC가 "<"로 설정

- 그렇지 않으면 CC가 "="로 설정

- RD m ? A [맨 오른쪽 바이트] ← 지정된 장치의 데이터(m)

- WD m ? 지정된 장치의 데이터 (m) ← A[맨 오른쪽 바이트]

- TD m ? (m)에 의해 지정된 장치가 데이터 바이트를 전송 및 수신 준비가 되었는지 테스트

- – I/O (Input and Output) 입출력

<간단한 예시>

SIC에서는 한번에 한 바이트씩 I/O 디바이스에 이동할 수 있음

이것이 레지스터 A에 저장되거나 A에서 꺼냄

Figure 1.2(a) – for SIC

LDA FIVE → FIVE를 레지스터 A에 저장

STA ALPHA → 레지스터 A에 있는 값을 ALPHA에 저장

LDCH CHARZ → 캐릭터 데이터를 레지스터에 저장

STCH C1 → 레지스터 A에 있는 데이터를 C1으로 이동

...

ALPHA RESW 1 → 상수 ALPHA 메모리에 1 할당

FIVE WORD 5 → 상수 FIVE 메모리에 5 할당

CHARZ BYTE C’Z’ → 상수 CHARZ 메모리에 C'Z' 할당

C1 RESB 1 → 상수 C1 메모리에 1 할당

상수 값을 정의하기 위한 구문

우측은 상수가 저장된 메모리 어드레스

중간은 메모리에 빈공간을 할당하기 위한 구문(RESW는 WORD, RESB는 BYTE)

오른쪽은 크기

'Computer Science > 시스템 프로그래밍' 카테고리의 다른 글

| SIC/XE Assembly Program with Object Code (0) | 2024.04.20 |

|---|---|

| 어셈블러의 작동과정 및 오브젝트 코드 생성 과정, 어셈블러 동작 메커니즘 (0) | 2024.04.19 |

| SIC/XE 아키텍처: 기본 구조에서 명령어 집합까지 (2) (0) | 2024.03.03 |

| SIC/XE 아키텍처: 기본 구조에서 명령어 집합까지 (1) (0) | 2024.03.03 |

| 시스템 프로그래밍과 컴퓨터 엔지니어링의 전반적인 소개 (0) | 2024.03.02 |